|

|

DVB-S demodulator / DSNG demodulator

Product code: CMS0048

The CMS0048 has been designed from the ground-up for high-speed and gate-efficient implementation on FPGA and ASIC platforms and offers very high performance when combined with either the integrated FEC decoder or an external advanced FEC decoder.

The demodulator provides an adaptable starting point for receiver sub-systems to be used in both the current and next-generation of digital TV set-top-boxes, VSAT terminals and related test and monitoring equipment.

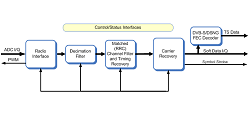

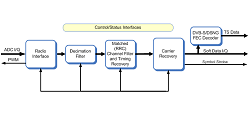

Block diagram

Click on diagram to enlarge

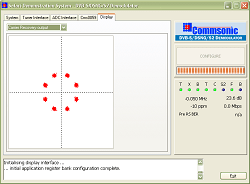

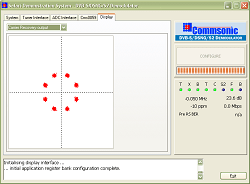

Safari Plug-in

Click on image for further information

|

Standards compliance

-

ETSI EN 301 210

-

ETSI EN 300 421

Features

-

Optional integrated FEC decoding.

-

Wide carrier acquisition range.

-

Automatic QAM mode, FEC and spectral inversion searching.

-

Programmable symbol rate recovery.

-

Real IF, zero-IF or near-zero-IF.

-

Variable ADC sampling frequency.

-

QPSK, 8PSK, 16-QAM.

Applications

-

ASICs for digital satellite TV reception.

-

High-end interactive satellite terminals.

-

Test, measurement and broadcast monitoring equipment.

-

Multi-standard, adaptable (software defined) receivers.

Implementation

-

Single external clock source.

-

Single external analogue AGC loop.

-

All-digital timing and carrier recovery.

-

Digital channel filtering.

-

Optimised for ASIC, Xilinx and Altera.

-

Evaluation boards available.

Plug-ins / Extensions

-

Group-delay equalisation.

|

Block diagram

Block diagram

Safari Plug-in

Safari Plug-in

Altera Megacore,

Altera Megacore,